Модуль керування (CTL)

Lw — машинна інструкція завантаження слова з комірки пам’яті до регістра; sw — машинна інструкція збереження вмістимого регістра у комірці пам’яті; beq -машинна інструкція умовного переходу за ознакою рівності. Для одноциклової машини достатньо мати комбінаційний пристрій керування. Адже кожна машинна інструкція одноразово вибирається з програмної пам’яті, а її код протягом цього циклу… Читати ще >

Модуль керування (CTL) (реферат, курсова, диплом, контрольна)

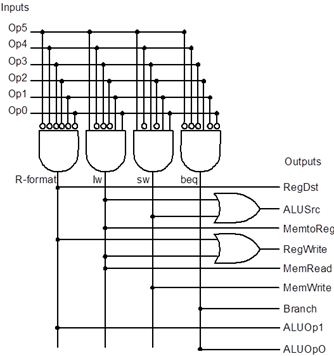

Для одноциклової машини достатньо мати комбінаційний пристрій керування. Адже кожна машинна інструкція одноразово вибирається з програмної пам’яті, а її код протягом цього циклу не змінюється.

— ctrl_chip.

library IEEE;

use IEEE. STD_LOGIC_1164.all;

use IEEE. STD_LOGIC_ARITH.all;

entity ctrl_chip is.

port (.

Op: in STD_LOGIC_VECTOR (5 downto 0);

RegDst: out STD_LOGIC;

ALUSrc: out STD_LOGIC;

MemWrite: out STD_LOGIC;

MemtoReg: out STD_LOGIC;

RegWrite: out STD_LOGIC;

Branch: out STD_LOGIC.

);

nd ctrl_chip;

-}} End of automatically maintained section.

rchitecture behav of ctl_chip is.

signal R_format, lw, sw, beq: std_logic;

begin.

R_format <= ((not Op (5)) and (not Op (4)) and (not Op (3)) and.

(not Op (2)) and (not Op (1)) and (not Op (0)));

lw <= (Op (5)) and (not Op (4)) and (not Op (3)) and.

(not Op (2)) and (Op (1)) and (Op (0));

sw <= (Op (5)) and (not Op (4)) and (Op (3)) and.

(not Op (2)) and (Op (1)) and (Op (0));

beq <= (not Op (5)) and (not Op (4)) and (not Op (3)) and.

(Op (2)) and (not Op (1)) and (not Op (0));

RegDst <= R_format;

ALUSrc <= lw or sw;

MemtoReg <= lw;

RegWrite <= R_format or lw;

MemWrite <= sw;

Branch <= beq;

end behav;

Рис. 6 Структура комбінаційного модуля керування: на вході - біти інструкції, на виході - біти керування.

Як R-format позначені машинні інструкції, що працюють з регістровими даними, наприклад: add r1, r2, r3;

lw — машинна інструкція завантаження слова з комірки пам’яті до регістра; sw — машинна інструкція збереження вмістимого регістра у комірці пам’яті; beq -машинна інструкція умовного переходу за ознакою рівності.

Перелічимо вихідні мікронакази, що генерує вузол керування: RegDest, ALUsrc, MemToReg, RegWrite, MtmRead, MemWrite, Branch, ALUOp1 та ALUOp2.