Паралельна передача даних

У сьомий рядку здійснюється пересилання даних з реєстра AX процесора в реєстр даних контролера А1. Процесор по шині адреси передає в контролер адресу А1, а по шині даних — байт даних, супроводжуючи їх сигналом «Висновок» (IOW #). Логіка управління контролера забезпечує запис даних із шини даних в реєстр даних А1 і встановлює в нуль біт готовності реєстра стану А2, формуючи тим самим керуючий… Читати ще >

Паралельна передача даних (реферат, курсова, диплом, контрольна)

Паралельна передача даних між контролером і ЗП є за своєю організацієюнайбільш простим способом обміну. Для організації паралельної передачіданих крім шини даних, кількість ліній в якій дорівнює числу одночаснопереданих бітів даних, використовується мінімальна кількість керуючих сигналів.

Для формування керуючого сигналу «Вихідні дані готові» і прийому з ЗП керуючого сигналу «Дані прийняті» в контролері використовується однорозрядних адресується реєстр стану й керування А2 (зазвичай використовуються роздільні реєстр стану і реєстр управління). Одночасно із записом чергового байта даних із шини даних системного інтерфейсу в адресується реєстр даних контролера (порт виводу А1) в реєстр стану й керування записується логічна одиниця. Тим самим формується керуючий сигнал «Вихідні дані готові» в шині зв’язку з ЗП.

ЗП, прийнявши байт даних, керуючим сигналом «Дані прийняті» обнуляє реєстр стану контролера. При цьому формуються керуючий сигнал системного інтерфейсу «Готовність ЗП» і ознака готовності ЗП до обміну, рухаючись в процесор по одній з ліній шини даних системного інтерфейсу за допомогою стандартної операції введення при реалізації програми асинхронного обміну.

Логіка управління контролера забезпечує селекцію адрес реєстрів контролера, прийом керуючих сигналів системного інтерфейсу і формування на їх основі внутрішніх керуючих сигналів контролера, формування керуючого сигналу системного інтерфейсу «Готовність ЗП» .Для сполучення реєстрів контролера з шинами адреси і даних системного інтерфейсу в контролері використовуються відповідно приймачі шини адреси і приймачі шини даних.

Розглянемо на прикладі, яким чином контролер ЗП забезпечує паралельну передачу даних в ЗП під управлінням програми асинхронного обміну.Алгоритм асинхронного обміну в даному випадку передачі простий.

- 1. Процесор мікроЕОМ перевіряє готовність ЗП до прийому даних.

- 2. Якщо ЗП готово до прийому даних (в даному випадку це логічний 0 в нульовому розряді реєстру А2), то дані передаються з шини даних системного інтерфейсу в реєстр даних А1 контролера і далі в ЗП. Інакше повторюється п. 1.

Приклад 1.1. Фрагмент програми передачі байта даних в асинхронному режимі з використанням паралельного контролера ЗП (Рис 1.5). Для написання програми асинхронної передачі скористаємося командами процесора 8086.

MOV. | DX, A2. | номер порта A2 вводимо в DX. |

m1:IN. | AL, DX. | читання байту з порта A2. |

TEST. | AL, 1. | перевірка нульового стану реєстру А2. |

JNS. | Ml. | перехід на мітку ml якщо розряд не нульовий. |

MOV. | AL, 64. | байт, що виводимо помістимо в AL. |

MOV. | DX, A1. | номер порта A1 вводимо в DX. |

OUT. | DX, AL. | вміст реєстра AX передаємо в порт A1. |

Команда у другому рядку призводить до наступних дій. При її виконанні процесор по шині адреси передає в контролер адресу А2, супроводжуючи його сигналом «Введення» (IORD #; тут і далі в дужках вказані сигнали на шині ISA). Логіка управління контролера, реагуючи на ці сигнали, забезпечує передачу в процесор вмісту реєстра стану А2 по шині даних системного інтерфейсу.

Команда в третьому рядку призводить до наступних дій. Процесор перевіряє значення відповідного розряду прийнятих даних. Нуль у цьому розряді вказує на неготовність ЗП до прийому даних і, отже, на необхідність повернення до перевірки вмісту А2, т. е. процесор, виконуючи три перші команди, очікує готовності ЗП до прийому даних. Одиниця в цьому розряді підтверджує готовність ЗП і, отже, можливість передачі байта даних.

У сьомий рядку здійснюється пересилання даних з реєстра AX процесора в реєстр даних контролера А1. Процесор по шині адреси передає в контролер адресу А1, а по шині даних — байт даних, супроводжуючи їх сигналом «Висновок» (IOW #). Логіка управління контролера забезпечує запис даних із шини даних в реєстр даних А1 і встановлює в нуль біт готовності реєстра стану А2, формуючи тим самим керуючий сигнал для ЗП «Вихідні дані готові». ЗП приймає байт даних і керуючим сигналом «Дані прийняті» встановлює в одиницю реєстр стану А2. (Далі контролер ЗП по цьому сигналу може сформувати і передати в процесор сигнал «Готовність ЗП», який в даному випадку сповіщає процесор про прийом даних зовнішнім пристроєм і дозволяє процесору зняти сигнал «Висновок» і тим самим завершити цикл виведення даних в команді пересилання, проте в IBM-сумісних персональних комп’ютерах з шиною ISA сигнал «Готовність ЗП» не формується, а є сигнал IO CH RDY #, що дозволяє продовжити цикл обміну, якщо пристрій недостатньо швидкий. В даному випадку немає необхідності в сигналі «Готовність ЗП», т.к. шина ISA є синхронної і, отже, всі операції виконуються по тактових імпульсах).

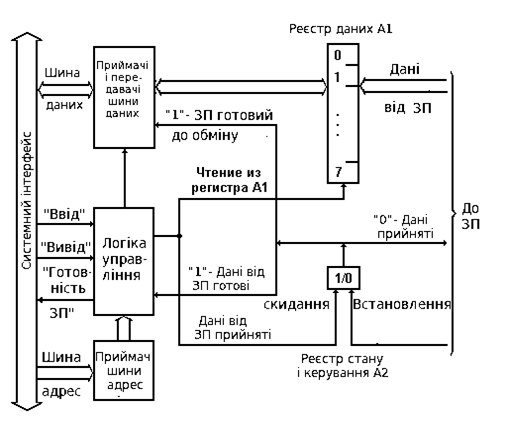

Блок-схема простого контролера ЗП, що забезпечує побайтно прийом даних з ЗП, наведена на Рис 1.6. У цьому контролері при взаємодії з зовнішнім пристроєм також використовуються два керуючих сигналу: «Дані від ЗП готові» і «Дані прийняті» .

Рис 1.6 Простий паралельний контролер вводу

Для формування керуючого сигналу «Дані прийняті» та прийому з ЗП керуючого сигналу «Дані від ЗП готові» використовується однорозрядних адресується реєстр стану й керування А2.

Зовнішній пристрій записує в реєстр даних контролера А1 черговий байт даних і керуючим сигналом «Дані від ЗП готові» встановлює в одиницю реєстр стану й керування А2.

При цьому формуються: керуючий сигнал системного інтерфейсу «Готовність ЗП», ознака готовності ЗП до обміну, рухаючись в процесор по одній з ліній шини даних системного інтерфейсу за допомогою операції введення при реалізації програми асинхронного обміну.

Тим самим контролер сповіщає процесор про готовність даних в реєстрі А1. Процесор, виконуючи програму асинхронного обміну, читає байт даних з реєстра даних контролера і обнуляє реєстр стану й керування А2. При цьому формується керуючий сигнал «Дані прийняті» в шині зв’язку із зовнішнім пристроєм.

Логіка управління контролера і приймачі шин системного інтерфейсу виконують ті ж функції, що і в контролері виводу (див. Рис 1.5), Розглянемо роботу паралельного інтерфейсу вводу при реалізації програми асинхронного обміну. Алгоритм асинхронного введення так само простий, як і асинхронного виведення.

- 1. Процесор перевіряє наявність даних в реєстрі даних контролера А1.

- 2. 2. Якщо дані готові (логічна 1 в реєстрі А2), то вони передаються з реєстра даних А1 на шину даних системного інтерфейсу і далі в реєстр процесора або елемент пам’яті мікрокомп'ютера. Інакше повторюється п. 1.

- 3. Приклад 1.2. Фрагмент програми прийому байта даних в асинхронному режимі з використанням паралельного інтерфейсу.

MOV. | DX, A2. | номер порта A2 вводимо в DX. |

m1:IN. | AL, DX. | читання байту з порта A2. |

TEST. | AL, 1. | перевірка нульового стану реєстру стану A2. |

JZ. | Ml. | перехід на мітку ml якщо розряд не нульовий. |

MOV. | DX, A1. | номер порта A1 вводимо в DX. |

IN. | AL, DX. | вміст реєстра A1 передаємо в реєстр AL. |

У третьому рядку виконується перевірка вмісту реєстра А2, тобто ознаки наявності даних в реєстрі даних А1. Команда виконується точно так само, як і в прикладі 2.1. Одиниця в нульовому розряді (вміст реєстра А2) підтверджує, що дані від ЗП записані в реєстр даних контролера і необхідно переслати їх на шину даних. Нуль в знаковому розряді вказує на неготовність даних від ЗП і, отже, на необхідність повернутися до перевірки готовності.

IN AL, DX — пересилання даних з реєстра даних контролера А1 в реєстр процесора AL. Процесор передає в контролер по шині адреси системного інтерфейсу адресу A1, супроводжуючи його сигналом «Введення». Логіка управління контролера у відповідь на сигнал «Введення» (IORD #) забезпечує передачу байта даних з реєстра даних А1 на шину даних і, в загальному випадку, але не в IBM-сумісному персональному комп’ютері із шиною ISA, супроводжує його сигналом «Готовність ЗП», який підтверджує наявність даних від ЗП на шині даних і за яким процесор зчитує байт із шини даних і поміщає його в зазначений реєстр. (В IBM-сумісному персональному комп’ютері із шиною ISA процесор зчитує байт із шини даних після закінчення певного часу після установки сигналу IORD #). Потім логіка управління обнуляє реєстр стану й керування А2, формуючи тим самим керуючий сигнал для зовнішнього пристрою «Дані прийняті» .Таким чином завершується цикл введення даних.

Як видно з розглянутих прикладів, для прийому або передачі одного байта даних процесору необхідно виконати всього кілька команд, час виконання яких і визначає максимально досяжну швидкість обміну даними при паралельній передачі. Таким чином, при паралельній передачі забезпечується досить висока швидкість обміну даними, яка обмежується тільки швидкодією ЗП.