Вихідні дані.

Розробка багатофункціонального блоку арифметико-логічного пристрою

Для арифметичних дій із словами великої довжини АЛУ включають послідовно. Сполучають вихід перенесення — C попередньої НС з входом перенесення C подальшої. Якщо пред’являються жорсткі вимоги до швидкодії ІС, то можлива організація прискореного перенесення з допомогою ІС типу ИП4 (мал. 2). Примітки Як відзначалося, числа в додатковому і в зворотному кодах пов’язані простим співвідношенням Nдоп… Читати ще >

Вихідні дані. Розробка багатофункціонального блоку арифметико-логічного пристрою (реферат, курсова, диплом, контрольна)

1. Склад функцій АЛУ визначається номером варіанту. Номер варіанту дорівнює порядковому номеру студента в списку групи з урахуванням порядкового номера групи.

Примітка. Знак * вказує на арифметичне складання.

Таблиця 1.1.

Варіант. | Виконувані блоком АЛП функції. | ||||||||||

A=B. |  A. | B. | |||||||||

| ; | ; | ; | ; |

- 2. Розрядність блоку АЛУ — 8 біт.

- 3. Кількість слів на вході АЛУ — 2

- 4. АЛУ повинне містити буфер результату операції.

- 5. Напруга живлення блоку АЛУ — +5 В.

Завдання.

- 1. Визначити варіант проекту і функції блоку АЛУ.

- 2. Розглянути теоретичні питання (АЛУ, суматори, регістри, структури ИМС К155ИПЗ, К155ИП4 і тому подібне).

- 3. Розробити структурну або функціональну схему блоку АЛУ.

- 4. Визначити елементну базу блоку АЛУ.

- 5. Розробити принципову електричну схему блоку АЛУ.

- 6. Розробити перелік елементів блоку АЛУ.

- 7. Розрахувати:

- * Максимальний час затримки блоку АЛУ.

- * Максимальну споживану потужність блоку АЛУ.

Оформити роботу відповідно до вимог БСКД.

Арифметико-логічний пристрій (АЛУ)

Це спеціалізовані мікросхеми, що виконують арифметичні або логічні операції над двома двійковими числами відповідно до програми (мал. 1).

Приклади ИМС серії ИПЗ, ИП4 і їх деякі параметри представлені в таблиці 1.2.

Таблиця 1.2.

Умовне позначення. | Р |   Число. | Виводи живлення. | |||

мВт. | НС. | НС. | вив.ИС. | + 5 В. | Загал. | |

1ЗЗИПЗ. | ||||||

134ИПЗ. | 180(400). | 180 (400). | ||||

К155 ИПЗ. | ||||||

530ИПЗ. | ||||||

К531ИПЗ. | ||||||

533ИПЗ. | ||||||

К555ИПЗ. | ||||||

КР531ИПЗ. | ||||||

КР1533ИПЗ. | ||||||

133ИП4. | ||||||

134ИП4. | ||||||

К155ИП4. | ||||||

КМ155ИП4. | ||||||

530ИП4. | ||||||

КМ555ИП4. | ; | ; | ; |

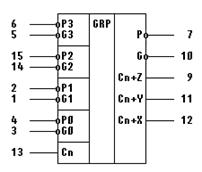

Рис. 2.1 Мікросхеми серії К155 ИП3 та ИП4

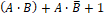

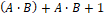

АЛУ типу ИПЗ (рис. 2.1) призначене для дій з двома чотирирозрядними двійковими словами:. Конкретний вид операції, що виконується мікросхемою, задається 5-розрядним кодом на входах М. Усього АЛУ може виконати 32 операції: 16 логічних (І, І-НЕ, АБО, ИЛИ-НЕ, що виключає АБО та ін.) і 16 арифметичних (складання, віднімання, подвоєння, порівняння чисел та ін.). Операції складання і віднімання проводяться з прискореним перенесенням з розряду в розряд. Крім того, є вхід прийому сигналу перенесення С. На виходах формуються результати логічних перетворень і арифметичних дій.

На виході перенесення С4 утворюється сигнал для старшого (п'ятого) розряду при виконанні арифметичних операцій. Додаткові виходи — утворення прискореного перенесення в і поширення прискореного перенесення Р. Вони використовуються при організації багато розрядних АЛУ у разі їх поєднання з блоком прискореного перенесення типу ИП4 (рис. 2.1).

Слова, А і В, що підлягають обробці, можуть бути представлені в позитивній або негативній логіці. Таблиці істинності для кожного варіанту логіки різні (таблиця. 1.3, 1.4). Щоб уникнути плутанини рівні сигналів позначені в них буквеними символами. Результати арифметичних операцій виражені в додатковому коді.

Таблиця 1.3.

Позитивна логіка. | ||||||

Логічні функції. | Арифметичні операції. | |||||

L. | L. | L. | L. | |||

L. | L. | L. | H. | |||

L. | L. | H. | L. | |||

L. | L. | H. | H. | 0 в кожному розряді. | 1 в кожному розряді. | 0 в кожному розряді. |

L. | H. | L. | L. | |||

L. | H. | L. | H. | |||

L. | H. | H. | L. | |||

L. | H. | H. | H. | |||

H. | L. | L. | L. | |||

H. | L. | L. | H. | |||

H. | L. | H. | L. | |||

H. | L. | H. | H. | |||

H. | H. | L. | L. | 1 у кожному розряді. | ||

H. | H. | L. | H. | |||

H. | H. | H. | L. | |||

H. | H. | H. | H. |

Таблиця 1.4.

Негативна логіка. | ||||||

Логічні функції. | Арифметичні операції. | |||||

L. | L. | L. | L. | |||

L. | L. | L. | H. | |||

L. | L. | H. | L. | |||

L. | L. | H. | H. | 0 в кожному розряді. | 1 в кожному розряді. | 0 в кожному розряді. |

L. | H. | L. | L. | |||

L. | H. | L. | H. | |||

L. | H. | H. | L. | |||

L. | H. | H. | H. | |||

H. | L. | L. | L. | |||

H. | L. | L. | H. | |||

H. | L. | H. | L. | |||

H. | L. | H. | H. | |||

H. | H. | L. | L. | 1 у кожному розряді. | ||

H. | H. | L. | H. | |||

H. | H. | H. | L. | |||

H. | H. | H. | H. |

Примітки Як відзначалося, числа в додатковому і в зворотному кодах пов’язані простим співвідношенням Nдоп= Nобр+ 1 або Nобр = Nдоп, — 1. Тому в тих рядках таблиці, де вказана операція «мінус 1», результат операції представлений в зворотному коді.

Старший розряд коду вибору операції (вхід Ь) визначає характер дій, виконуваних АЛУ. Коли на цьому вході сигнал високого рівня, АЛУ робить логічні операції порозрядних над кожною парою біт слів, А і В. Внутрішнє перенесення між розрядами в цьому режимі не діє. Арифметичні операції виконуються, коли на вході М діє низький потенціал, який є також дозволяючим сигналом для перенесення між розрядами. Вихідний сигнал формується з урахуванням стану входу перенесення. Обидва сигнали перенесення — вхідний C і вихідний C4 — інверсні відносно сигналів на входах, А і В, тобто коли слова, А і В — в позитивній логіці, сигналу перенесення відповідає низький рівень напруги на відповідному виводі, а в негативній логіці — навпаки.

АЛУ виконує арифметико-логічну операцію, логічна операція реалізується порозрядно, а арифметична — з перенесенням. Наприклад, вхідному коду М = L H H L H відповідає операція А*В плюс А, де А*В — логічне множення двох слів. Якщо, А = 1010(2) і В = 0111(2), то перша операція дає А*В = 1010(2> і, отже, 0010(2) плюс 1010<2) — 1100а).

При використанні АЛУ як компаратор, сигнал знімають з виходу, А = В (висновок 14). Цей вихід з відкритим колектором, і його слід підключати до джерела живлення через зовнішній резистор 1 кОм. Коли числа, А і В рівні, на виході А = А формується сигнал високого рівня. Одночасно сигнал на виході С4 (контакт 16) характеризує співвідношення між числами, А і В (таблиця. 5).

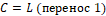

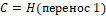

Для арифметичних дій із словами великої довжини АЛУ включають послідовно. Сполучають вихід перенесення — C попередньої НС з входом перенесення C подальшої. Якщо пред’являються жорсткі вимоги до швидкодії ІС, то можлива організація прискореного перенесення з допомогою ІС типу ИП4 (мал. 2).

В цьому випадку час виконання операції над 16-розрядними числами складе. Виходи перенесення Р і G ІС типу ИП4 використовуються для утворення групового перенесення.

Таблиця 1.5.

Віхдний код. | Вид логіки. | Стан входів. |

Позитивна. | ||

Негативна. |